Overview

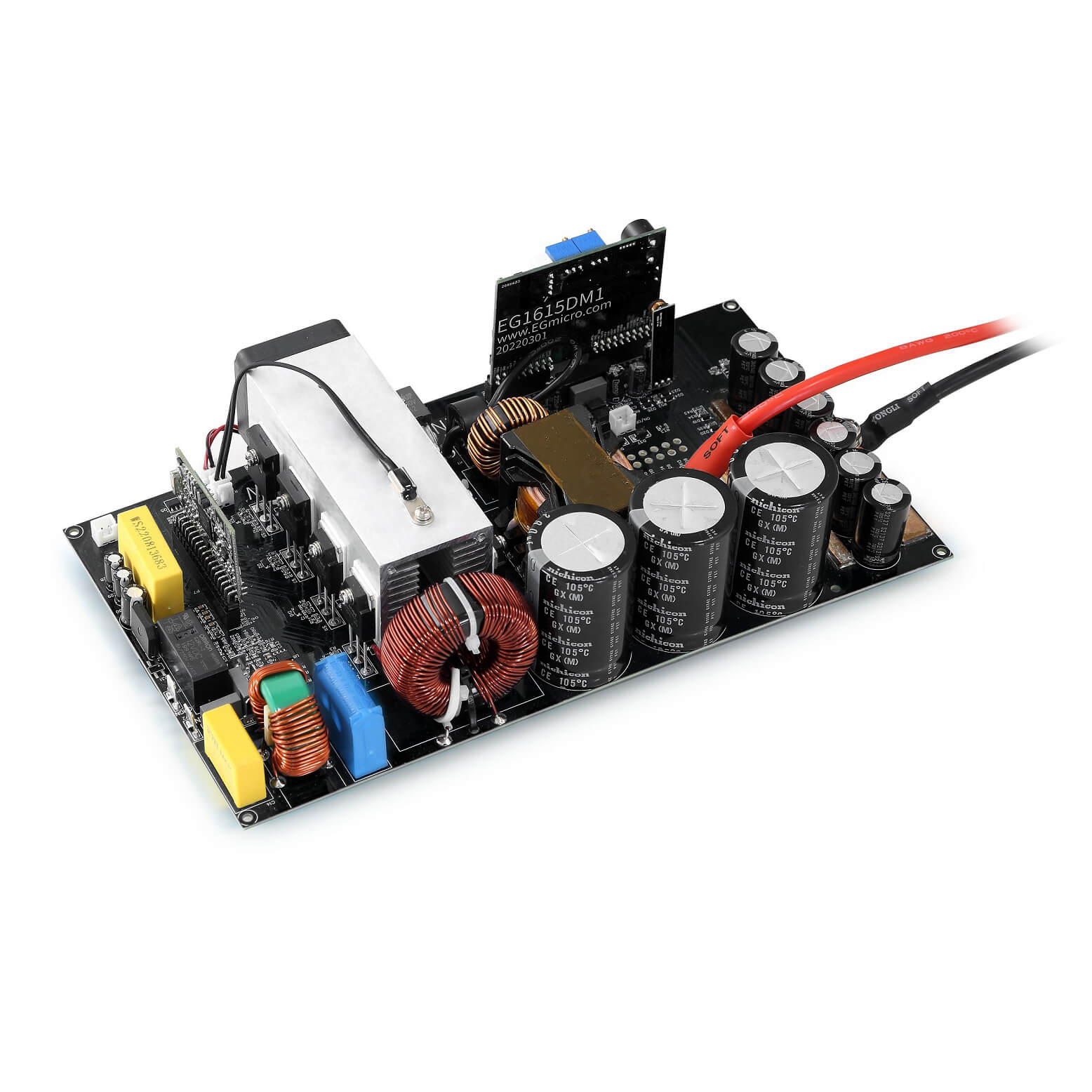

- Electronic components material purchasing.

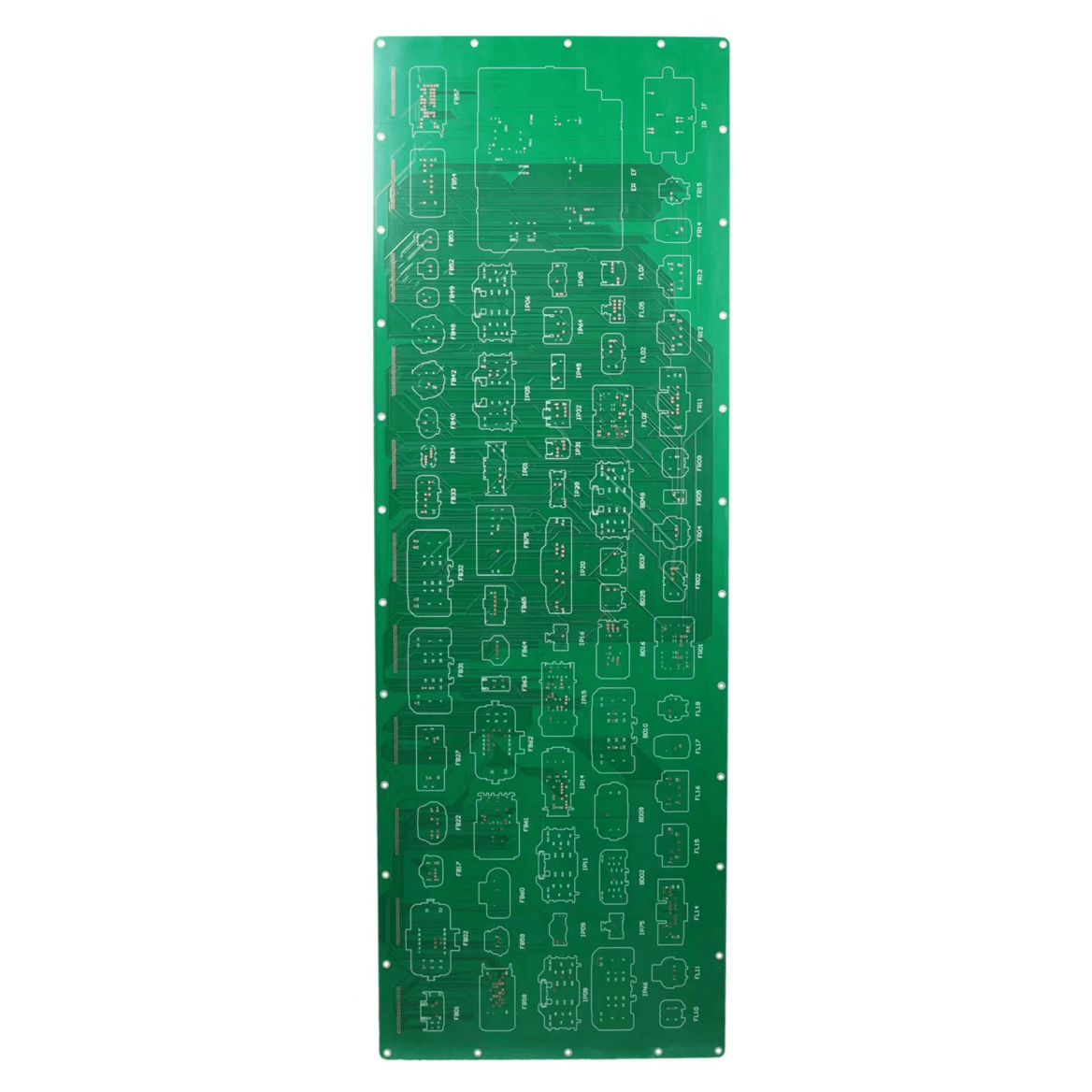

- Bare PCB fabrication.

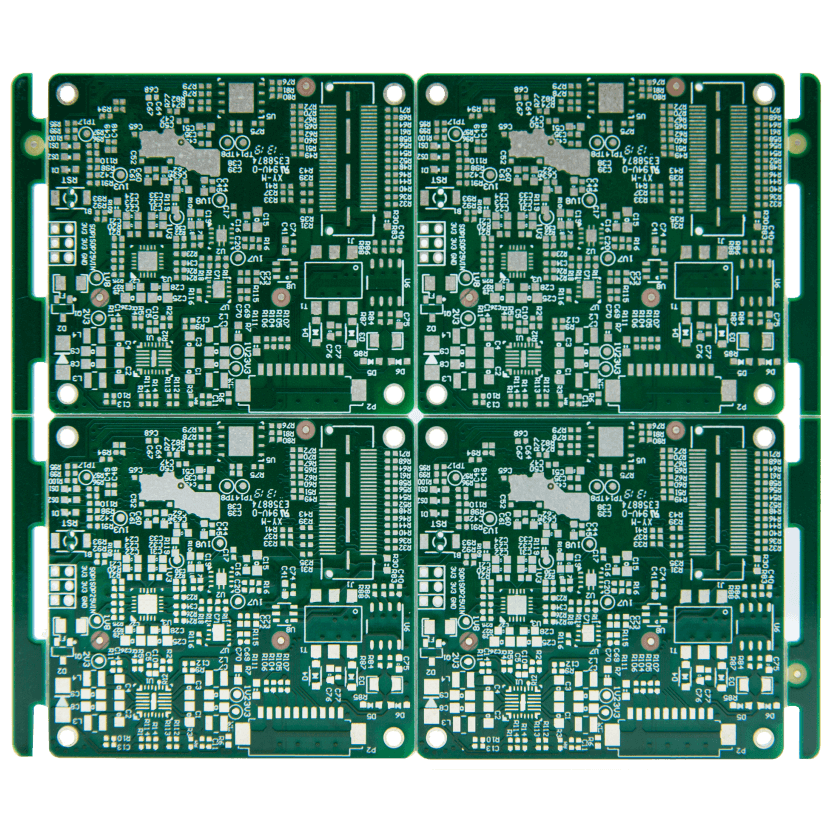

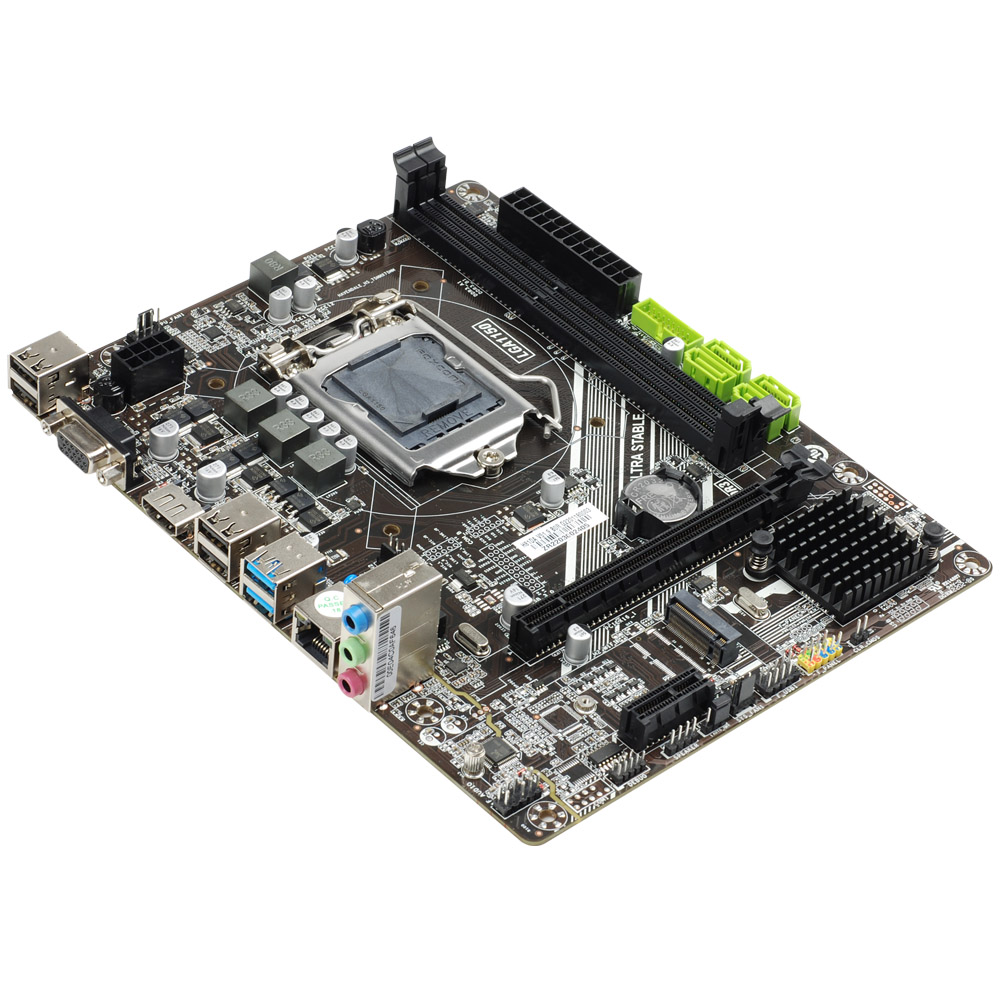

- PCB Assembly Service. (SMT, BGA, DIP).

- FULL Test: AOI, In-Circuit Test (ICT), Functioal Test (FCT).

- Cable, Wire-harness assembly,sheet metal,Electrical cabinet Assembly service.

- Conformal coating service.

- Prototyping and mass production...

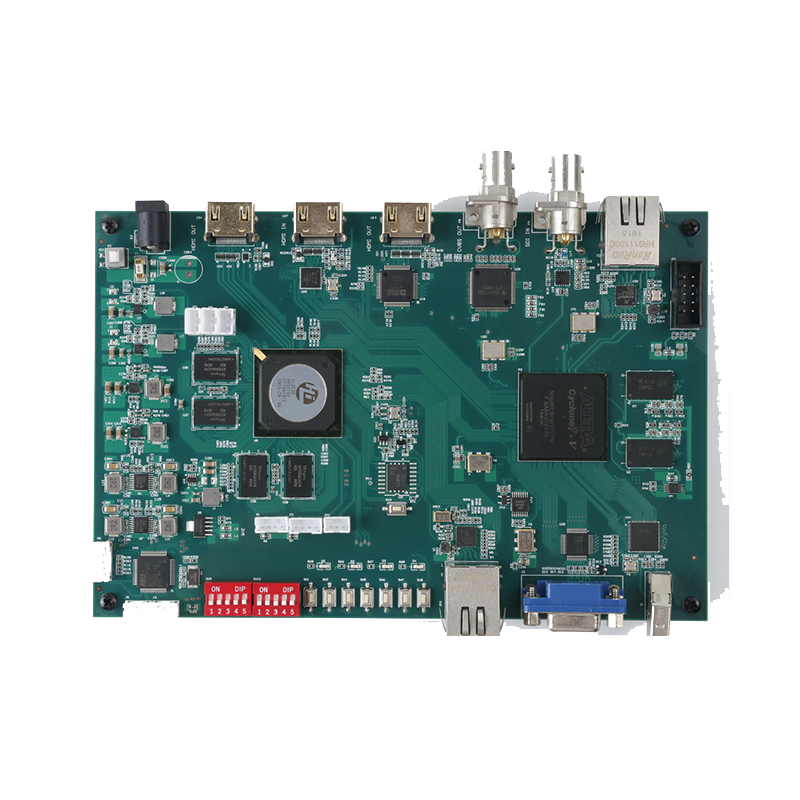

- Interface level: The corresponding position can be adjusted by magnetic beads.

- Core board power supply: 5-12V power supply generates two power supply through the T1 chip LTM4628 to meet the FPGA current requirements

- Core board startup method: JTAG, QSPIFLASH

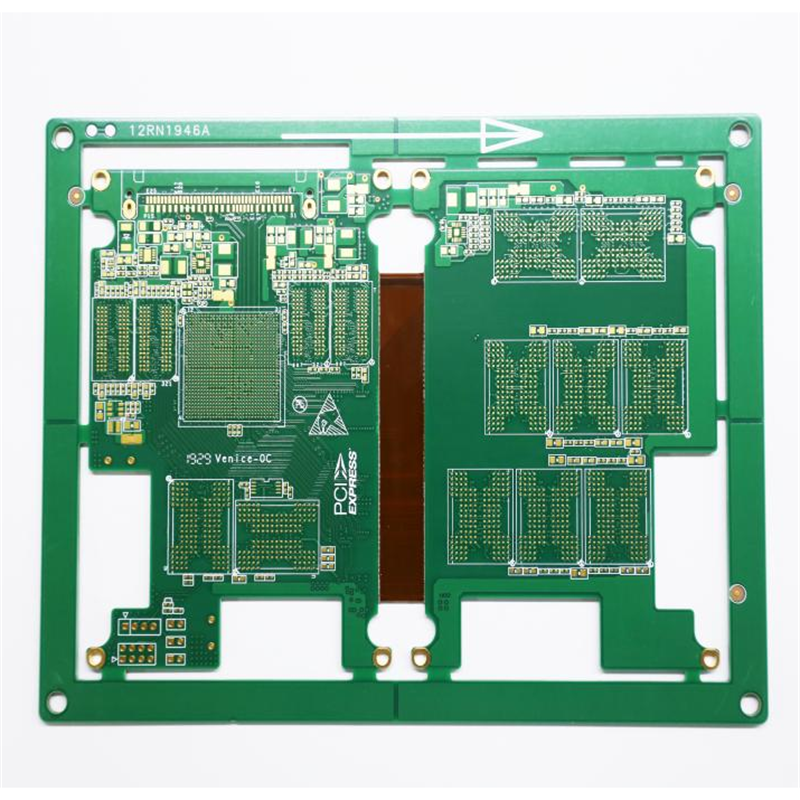

- Connector tube foot definition: 4 high -speed extensions, 120pin Panasonic AXK5A2137yg

- The bottom plate SFP interface: 4 optical modules can achieve high -speed optical fiber communication, with a speed of up to 10GB/s

- Fave Plate GXB clock: The bottom plate provides a 200MHz reference clock for the GXB transceiver

- The bottom plate 40 -needle extension: reserved 2 2.54mm standard 40 -pin extension J11 and J12, which is used to connect the modules designed by the company or the module function circuit designed by the user themselves

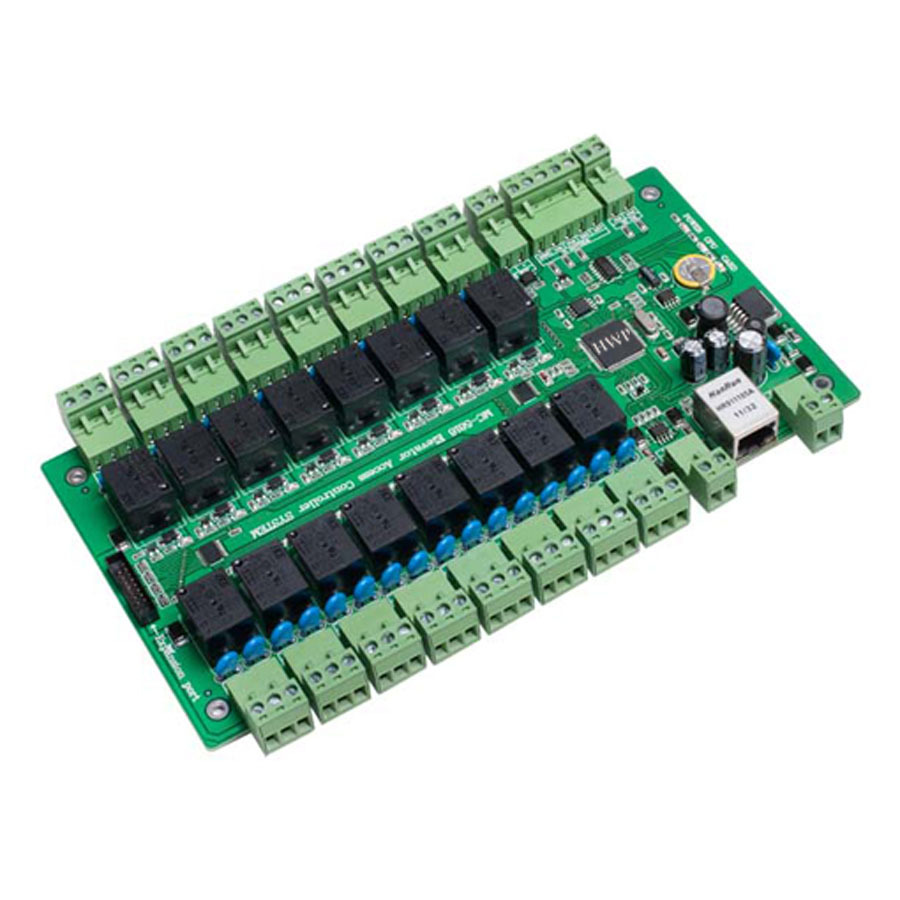

- Electronic components material purchasing.

- Bare PCB fabrication.

- PCB Assembly Service. (SMT, BGA, DIP).

- FULL Test: AOI, In-Circuit Test (ICT), Functioal Test (FCT).

- Cable, Wire-harness assembly,sheet metal,Electrical cabinet Assembly service.

- Conformal coating service.

- Prototyping and mass production...

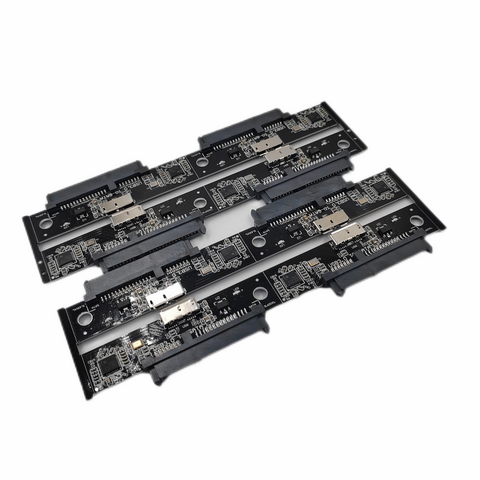

- Electronic components material purchasing.

- Bare PCB fabrication.

- PCB Assembly Service. (SMT, BGA, DIP).

- FULL Test: AOI, In-Circuit Test (ICT), Functioal Test (FCT).

- Cable, Wire-harness assembly,sheet metal,Electrical cabinet Assembly service.

- Conformal coating service.

- Prototyping and mass production...

FAQs

Detailed Information

- Core plate clock: multiple clock sources on board. This includes 100MHz system clock source 510kba100M000bag CMOS crystal 125MHz Transceiver Differential Clock Sittaid Sit9102 Crystal 300MHz DDR4's external differential clock source SIT9102 crystal.

- JTAG debug port: MP5652 core board has a 6PIN patch JTAG download debugging interface.

- Convenient for users to debug FPGA separately.

- System reset: At the same time, the button also provides the system with the global reset signal MP5652 core board to support the power -on reset. The entire chip is reset.

- LED: There are 4 red LED lights on the core board, one of which is DDR4 reference power indicator.

- Button and switch: There are 4 keys on the bottom plate, which is connected to the corresponding pipe foot on the J2 connector.

- Usually high level, pressing to low level